## SINGLE-ENDED ANALOG-INPUT 24-BIT, 96-kHz STEREO A/D CONVERTER

#### **FEATURES**

- 24-Bit Delta-Sigma Stereo A/D Converter

- Single-Ended Voltage Input: 3 V p-p

- Antialiasing Filter Included

- Oversampling Decimation Filter

- Oversampling Frequency: ×64, ×128

- Pass-Band Ripple: ±0.05 dB

Stop-Band Attenuation: -65 dB

- On-Chip High-Pass Filter (HPF): 0.84 Hz (44.1 kHz)

- High Performance

- THD+N: 96 dB (Typical)SNR: 105 dB (Typical)

- Dynamic Range: 105 dB (Typical)

- PCM Audio Interface

- Master/Slave Mode Selectable

- Data Formats: 24-Bit Left-Justified; 24-Bit I<sup>2</sup>S; 20-, 24-Bit Right-Justified

- Sampling Rate: 16 kHz to 96 kHz

- System Clock: 256 f<sub>S</sub>, 384 f<sub>S</sub>, 512 f<sub>S</sub>, 768 f<sub>S</sub>

- Dual Power Supplies: 5 V for Analog, 3.3 V for

- Digital

- Package: 20-Pin SSOP

#### **APPLICATIONS**

- AV Amplifier Receiver

- MD Player

- CD Recorder

- Multitrack Receiver

- Electric Musical Instrument

#### DESCRIPTION

The PCM1802 is a high-performance, low-cost, single-chip stereo analog-to-digital converter with single-ended analog voltage input. The PCM1802 uses a delta-sigma modulator with 64- or 128-times oversampling, and includes a digital decimation filter and high-pass filter (HPF), which removes the dc component of the input signal. For various applications, the PCM1802 supports master and slave modes and four data formats in serial interface. The PCM1802 is suitable for a wide variety of cost-sensitive consumer applications where good performance, 5-V analog supply, and 3.3-V digital supply operation is required. The PCM1802 is fabricated using a highly advanced CMOS process and is available in the DB 20-pin SSOP package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

System Two, Audio Precision are trademarks of Audio Precision. All other trademarks are the property of their respective owners.

This device contains circuits to protect its inputs and outputs against damage due to high static voltages or electrostatic fields. These circuits have been qualified to protect this device against electrostatic discharges (ESD) of up to 2 kV according to MIL-STD-883C, Method 3015; however, it is advised that precautions be taken to avoid application of any voltage higher than maximum-rated voltages to these high-impedance circuits. During storage or handling, the device leads should be shorted together or the device should be placed in conductive foam. In a circuit, unused inputs should always be connected to an appropriated logic voltage level, preferably either  $V_{\rm CC}$  or ground. Specific guidelines for handling devices of this type are contained in the publication *Electrostatic Discharge (ESD)* (SSYA010) available from Texas Instruments.

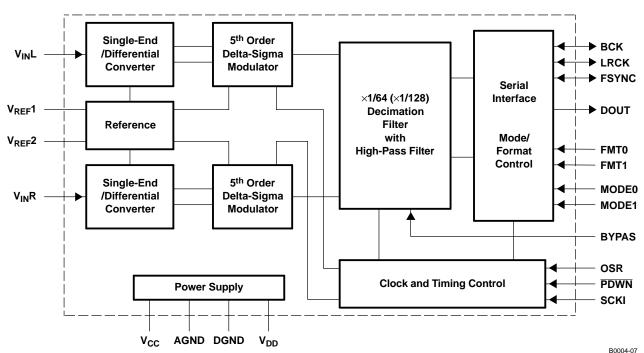

#### PIN ASSIGNMENTS

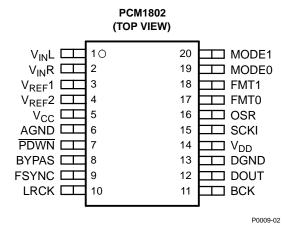

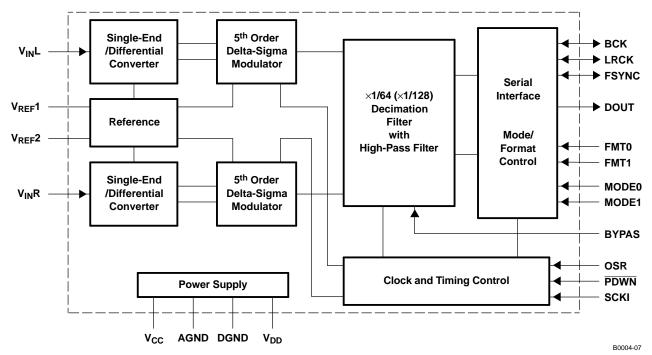

#### **BLOCK DIAGRAM**

#### **Terminal Functions**

| TERMINAL           |     | I/O | DESCRIPTIONS                                                                                                            |  |  |  |

|--------------------|-----|-----|-------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME               | PIN | 1/0 | DESCRIPTIONS                                                                                                            |  |  |  |

| AGND               | 6   | _   | Analog GND                                                                                                              |  |  |  |

| BCK                | 11  | I/O | Bit clock input/output <sup>(1)</sup>                                                                                   |  |  |  |

| BYPAS              | 8   | I   | HPF bypass control. Low: normal mode (dc cut); High: bypass mode (through) (2)                                          |  |  |  |

| DGND               | 13  | _   | Digital GND                                                                                                             |  |  |  |

| DOUT               | 12  | 0   | Audio data output                                                                                                       |  |  |  |

| FMT0               | 17  | I   | Audio data format select 0. See data format <sup>(2)</sup>                                                              |  |  |  |

| FMT1               | 18  | I   | Audio data format select 1. See data format <sup>(2)</sup>                                                              |  |  |  |

| FSYNC              | 9   | I/O | Frame synchronous clock input/output <sup>(1)</sup>                                                                     |  |  |  |

| LRCK               | 10  | I/O | Sampling clock input/output <sup>(1)</sup>                                                                              |  |  |  |

| MODE0              | 19  | I   | Mode select 0. See interface mode <sup>(2)</sup>                                                                        |  |  |  |

| MODE1              | 20  | I   | Mode select 1. See interface mode <sup>(2)</sup>                                                                        |  |  |  |

| OSR                | 16  | I   | Oversampling ratio select. Low: ×64 f <sub>S</sub> ; High: ×128 f <sub>S</sub> <sup>(2)</sup>                           |  |  |  |

| PDWN               | 7   | I   | Power-down control, active-low <sup>(2)</sup>                                                                           |  |  |  |

| SCKI               | 15  | I   | System clock input; 256 f <sub>S</sub> , 384 f <sub>S</sub> , 512 f <sub>S</sub> , or 768 f <sub>S</sub> <sup>(3)</sup> |  |  |  |

| V <sub>CC</sub>    | 5   | _   | Analog power supply, 5 V                                                                                                |  |  |  |

| $V_{DD}$           | 14  | _   | Digital power supply, 3.3 V                                                                                             |  |  |  |

| $V_{IN}L$          | 1   | I   | Analog input, L-channel                                                                                                 |  |  |  |

| V <sub>IN</sub> R  | 2   | ı   | Analog input, R-channel                                                                                                 |  |  |  |

| V <sub>REF</sub> 1 | 3   | -   | Reference-1 decoupling capacitor                                                                                        |  |  |  |

| V <sub>REF</sub> 2 | 4   | -   | Reference-2 voltage input, normally connected to V <sub>CC</sub>                                                        |  |  |  |

- Schmitt-trigger input

- (2) (3) Schmitt-trigger input with internal pulldown (50 k $\Omega$  typically), 5-V tolerant Schmitt-trigger input, 5-V tolerant

## **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted) (1)

| Supply voltage                           | V <sub>CC</sub>                                                              | 6.5 V                                         |

|------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------|

|                                          | $V_{DD}$                                                                     | 4 V                                           |

| Ground voltage differences               | AGND, DGND                                                                   | ±0.1 V                                        |

| Supply voltage difference                | $V_{CC}, V_{DD}$                                                             | $V_{CC} - V_{DD} < 3.0 \text{ V}$             |

| Digital input voltage                    | FSYNC, LRCK, BCK, DOUT                                                       | -0.3 V to (V <sub>DD</sub> + 0.3 V)           |

|                                          | PDWN, BYPAS, SCKI, OSR, FMT0, FMT1, MODE0, MODE1                             | -0.3 V to 6.5 V                               |

| Analog input voltage                     | V <sub>IN</sub> L, V <sub>IN</sub> R, V <sub>REF</sub> 1, V <sub>REF</sub> 2 | $-0.3 \text{ V to } (V_{CC} + 0.3 \text{ V})$ |

| Input current (any pins except supplies) |                                                                              | ±10 mA                                        |

| Ambient temperature under bias           |                                                                              | -40°C to 125°C                                |

| Storage temperature                      |                                                                              | –55°C to 150°C                                |

| Junction temperature                     |                                                                              | 150°C                                         |

| Lead temperature (soldering)             |                                                                              | 260°C, 5 s                                    |

| Package temperature (IR reflow, peak)    |                                                                              | 260°C                                         |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

all specifications at  $T_A$  = 25°C,  $V_{CC}$  = 5 V,  $V_{DD}$  = 3.3 V, master mode,  $f_S$  = 44.1 kHz, system clock = 384  $f_S$ , oversampling ratio = ×128, 24-bit data (unless otherwise noted)

|                                |                                   | TEST CONDITIONS                                        |        | PCM1802DB                                        |          |       |  |

|--------------------------------|-----------------------------------|--------------------------------------------------------|--------|--------------------------------------------------|----------|-------|--|

|                                |                                   | TEST CONDITIONS                                        | MIN    | MIN TYP MAX                                      |          | UNIT  |  |

|                                | Resolution                        |                                                        |        | 24                                               |          | Bits  |  |

| DATA F                         | ORMAT                             |                                                        |        |                                                  |          |       |  |

|                                | Audio data interface format       |                                                        |        | eft-justified, l <sup>2</sup><br>right-justified |          |       |  |

|                                | Audio data bit length             |                                                        |        | 20, 24                                           |          | Bits  |  |

|                                | Audio data format                 |                                                        | MSB fi | rst, 2s comp                                     | lement   |       |  |

| $f_S$                          | Sampling frequency                |                                                        | 16     | 44.1                                             | 96       | kHz   |  |

|                                |                                   | 256 f <sub>S</sub>                                     | 4.096  | 11.2896                                          | 24.576   |       |  |

|                                | System clock frequency            | 384 f <sub>S</sub>                                     | 6.144  | 16.9344                                          | 36.864   | NALI- |  |

|                                | System clock frequency            | 512 f <sub>S</sub>                                     | 8.192  | 22.5792                                          | 49.152   | MHz   |  |

|                                |                                   | 768 f <sub>S</sub>                                     | 12.288 | 33.8688                                          | (1)      |       |  |

| INPUT L                        | .OGIC                             |                                                        | ·      |                                                  |          |       |  |

| V <sub>IH</sub> <sup>(2)</sup> |                                   |                                                        | 2      |                                                  | $V_{DD}$ |       |  |

| V <sub>IL</sub> <sup>(2)</sup> |                                   |                                                        | 0      |                                                  | 0.8      | VDC   |  |

| V <sub>IH</sub> <sup>(3)</sup> | Input logic level                 |                                                        | 2      |                                                  | 5.5      |       |  |

| V <sub>IL</sub> (3)            |                                   |                                                        | 0      |                                                  | 0.8      |       |  |

| I <sub>IH</sub> (4)            |                                   | $V_{IN} = V_{DD}$                                      |        |                                                  | ±10      |       |  |

| I <sub>IL</sub> (4)            | Innut logic current               | V <sub>IN</sub> = 0 V                                  |        |                                                  | ±10      | μA    |  |

| I <sub>IH</sub> (5)            | Input logic current               | $V_{IN} = V_{DD}$                                      |        | 65                                               | 100      |       |  |

| I <sub>IL</sub> (5)            |                                   | V <sub>IN</sub> = 0 V                                  |        |                                                  | ±10      |       |  |

| OUTPU                          | LOGIC                             |                                                        |        |                                                  |          |       |  |

| V <sub>OH</sub> <sup>(6)</sup> | Outrot le sie level               | I <sub>OUT</sub> = -1 mA                               | 2.8    |                                                  |          | \/DC  |  |

| V <sub>OL</sub> (6)            | Output logic level                | I <sub>OUT</sub> = 1 mA                                |        |                                                  | 0.5      | VDC   |  |

| DC ACC                         | URACY                             |                                                        | ·      |                                                  |          |       |  |

|                                | Gain mismatch, channel-to-channel |                                                        |        | ±1                                               | ±4       | %FSF  |  |

|                                | Gain error                        |                                                        |        | ±2                                               | ±6       | %FSF  |  |

|                                | Bipolar zero error                | HPF bypassed <sup>(7)</sup>                            |        | ±2                                               |          | %FSF  |  |

| DYNAM                          | IC PERFORMANCE (8)                |                                                        | ·      |                                                  |          |       |  |

|                                |                                   | $f_S = 44.1 \text{ kHz}, V_{IN} = -0.5 \text{ dB}$     |        | 0.0015%                                          | 0.003%   |       |  |

| TUD.N                          | Total harmania distantian , naisa | $f_S = 96 \text{ kHz}, V_{IN} = -0.5 \text{ dB}^{(9)}$ |        | 0.0025%                                          |          |       |  |

| I HD+N                         | Total harmonic distortion + noise | $f_S = 44.1 \text{ kHz}, V_{IN} = -60 \text{ dB}$      |        | 0.7%                                             |          |       |  |

|                                |                                   | $f_S = 96 \text{ kHz}, V_{IN} = -60 \text{ dB}^{(9)}$  |        | 1.2%                                             |          |       |  |

|                                | Dimomia rongo                     | f <sub>S</sub> = 44.1 kHz, A-weighted                  | 100    | 105                                              |          | 10    |  |

|                                | Dynamic range                     | f <sub>S</sub> = 96 kHz, A-weighted <sup>(9)</sup>     |        | 103                                              |          | dB    |  |

|                                | C/N                               | f <sub>S</sub> = 44.1 kHz, A-weighted                  | 100    | 105                                              |          | j.    |  |

|                                | S/N ratio                         | f <sub>S</sub> = 96 kHz, A-weighted <sup>(9)</sup>     |        | 103                                              |          | dB    |  |

- (1) Maximum system clock frequency is not applicable at 768 f<sub>S</sub>, f<sub>S</sub> = 96 kHz. See the System Clock section of this data sheet.

- Pins 9–11: FSYNC, LRCK, BCK (Schmitt-trigger input in slave mode)

Pins 7–8, 15–20: PDWN, BYPAS, SCKI, OSR, FMT0, FMT1, MODE0, MODE1 (Schmitt-trigger input, 5-V tolerant)

- Pins 9–11, 15: FSYNC, LRCK, BCK (Schmitt-trigger input in slave mode), SCKI (Schmitt-trigger input)

Pins 7–8, 16–20: PDWN, BYPAS, OSR, FMT0, FMT1, MODE0, MODE1 (Schmitt-trigger input, with 50-kΩ typical pulldown resistor)

- Pins 9-12: FSYNC, LRCK, BCK (in master mode), DOUT

- High-pass filter (7)

- Analog performance specifications are tested with System Two™ audio measurement system by Audio Precision™, using 400-Hz HPF, 20-kHz LPF for 44.1-kHz operation, 40-kHz LPF for 96-kHz operation in RMS mode.

- (9) $f_S = 96$  kHz, system clock = 256  $f_S$ , oversampling ratio =  $\times 64$ .

## **ELECTRICAL CHARACTERISTICS (continued)**

all specifications at  $T_A = 25^{\circ}C$ ,  $V_{CC} = 5$  V,  $V_{DD} = 3.3$  V, master mode,  $f_S = 44.1$  kHz, system clock = 384  $f_S$ , oversampling ratio =  $\times 128$ , 24-bit data (unless otherwise noted)

|                 |                                        | TEST CONDITIONS                                                               | F                    | UNIT                 |                      |      |

|-----------------|----------------------------------------|-------------------------------------------------------------------------------|----------------------|----------------------|----------------------|------|

|                 |                                        | TEST CONDITIONS                                                               | MIN                  | TYP                  | MAX                  | UNII |

|                 | Observation and the                    | f <sub>S</sub> = 44.1 kHz                                                     | 96                   | 103                  |                      | Ē    |

|                 | Channel separation                     | f <sub>S</sub> = 96 kHz <sup>(9)</sup>                                        |                      | 98                   |                      | dB   |

| ANAL            | OG INPUT                               |                                                                               |                      |                      |                      |      |

|                 | Input voltage                          |                                                                               |                      | 0.6 V <sub>CC</sub>  |                      | Vp-p |

|                 | Center voltage (V <sub>REF</sub> 1)    |                                                                               |                      | 0.5 V <sub>CC</sub>  |                      | V    |

|                 | Input impedance                        |                                                                               |                      | 20                   |                      | kΩ   |

|                 | Antialiasing filter frequency response | -3 dB                                                                         |                      | 300                  |                      | kHz  |

| DIGIT           | AL FILTER PERFORMANCE                  |                                                                               |                      |                      |                      |      |

|                 | Pass band                              |                                                                               |                      |                      | 0.454 f <sub>S</sub> | Hz   |

|                 | Stop band                              |                                                                               | 0.583 f <sub>S</sub> |                      |                      | Hz   |

|                 | Pass-band ripple                       |                                                                               |                      |                      | ±0.05                | dB   |

|                 | Stop-band attenuation                  |                                                                               | -65                  |                      |                      | dB   |

|                 | Delay time                             |                                                                               |                      | 17.4/f <sub>S</sub>  |                      | s    |

|                 | HPF frequency response                 | -3 dB                                                                         |                      | 0.019 f <sub>S</sub> |                      | mHz  |

| POWE            | ER SUPPLY REQUIREMENTS                 |                                                                               |                      |                      |                      |      |

| $V_{CC}$        | Voltage renge                          |                                                                               | 4.5                  | 5                    | 5.5                  | VDC  |

| $V_{DD}$        | Voltage range                          |                                                                               | 2.7                  | 3.3                  | 3.6                  | VDC  |

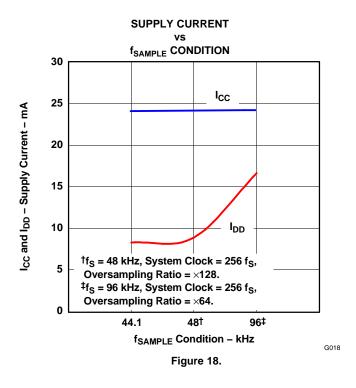

| I <sub>CC</sub> |                                        | V <sub>CC</sub> = 5 V, V <sub>DD</sub> = 3.3 V                                |                      | 24                   | 30                   |      |

|                 | Supply current (10)                    | $f_S = 44.1 \text{ kHz V}_{CC} = 5 \text{ V}, \text{ V}_{DD} = 3.3 \text{ V}$ |                      | 8.3                  | 10                   | mA   |

| I <sub>DD</sub> |                                        | $f_S = 96 \text{ kHz}, V_{CC} = 5 \text{ V}, V_{DD} = 3.3 \text{ V}^{(8)}$    |                      | 17                   |                      |      |

|                 | Davier dissination, ensembles          | f <sub>S</sub> = 44.1 kHz, V <sub>CC</sub> = 5 V, V <sub>DD</sub> = 3.3 V     |                      | 147                  | 183                  | \^/  |

| $P_D$           | Power dissipation; operation           | $f_S = 96 \text{ kHz}, V_{CC} = 5 \text{ V}, V_{DD} = 3.3 \text{ V}^{(8)}$    |                      | 176                  |                      | mW   |

|                 | Power dissipation; power down          | V <sub>CC</sub> = 5 V, V <sub>DD</sub> = 3.3 V                                |                      | 0.5                  |                      | mW   |

| TEMP            | ERATURE RANGE                          |                                                                               |                      |                      |                      |      |

|                 | Operation temperature                  |                                                                               | -40                  |                      | 85                   | °C   |

|                 | Thermal resistance (θ <sub>JA</sub> )  | 20-pin SSOP                                                                   |                      | 115                  |                      | °C/W |

<sup>(10)</sup> Minimum load on DOUT (pin 12), BCK (pin 11), LRCK (pin 10), FSYNC (pin 9)

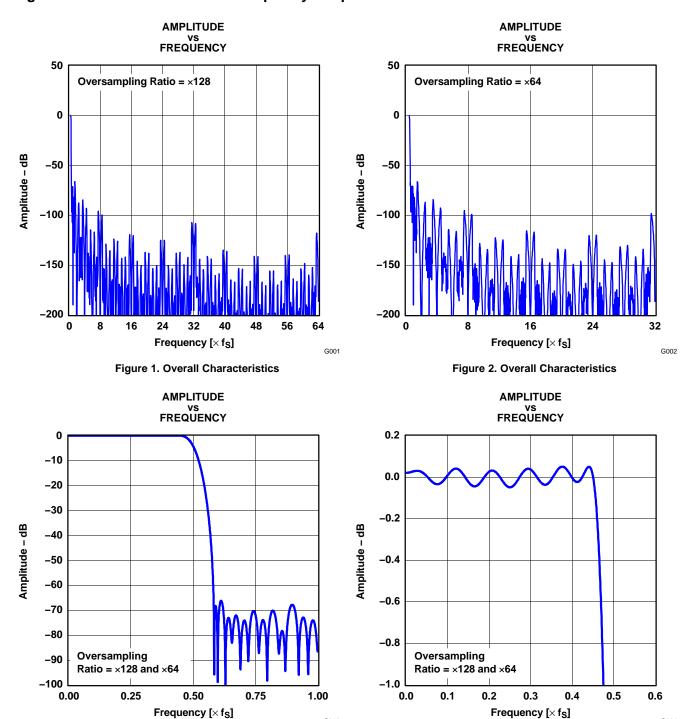

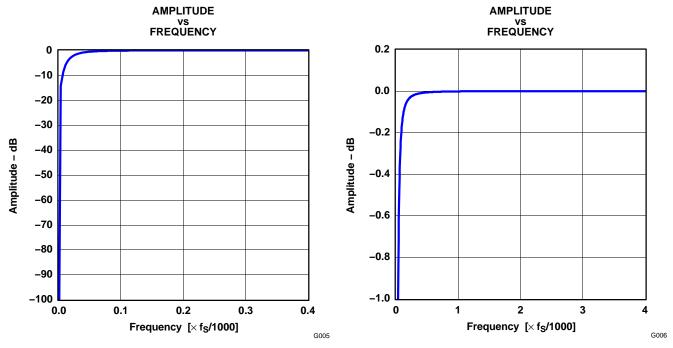

## TYPICAL PERFORMANCE CURVES OF INTERNAL FILTER

## Digital Filter—Decimation Filter Frequency Response

Figure 3. Stop-Band Attenuation Characteristics

Figure 4. Pass-Band Ripple Characteristics

G004

All specifications at  $T_A$  = 25°C,  $V_{CC}$  = 5 V,  $V_{DD}$  = 3.3 V, master mode,  $f_S$  = 44.1 kHz, system clock = 384  $f_S$ , oversampling ratio =  $\times$ 128, 24-bit data, unless otherwise noted.

G003

# TYPICAL PERFORMANCE CURVES OF INTERNAL FILTER (continued) HPF (High-Pass Filter) Frequency Response

Figure 5. HPF Stop-Band Characteristics

Figure 6. HPF Pass-Band Characteristics

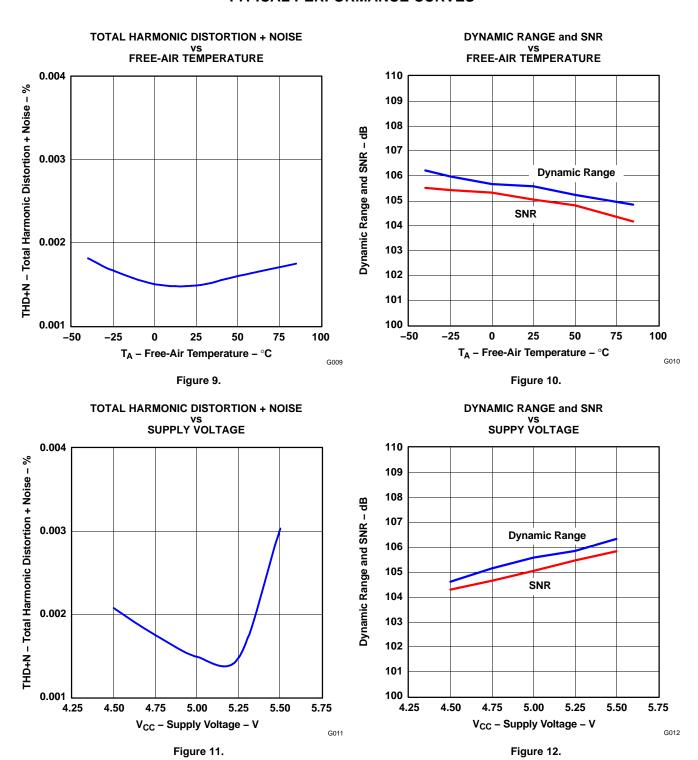

## Analog Filter—Antialiasing Filter Frequence Response

Figure 7. Antialias Filter Stop-Band Characteristics

Figure 8. Antialias Filter Pass-Band Characteristics

All specifications at  $T_A$  = 25°C,  $V_{CC}$  = 5 V,  $V_{DD}$  = 3.3 V, master mode,  $f_S$  = 44.1 kHz, system clock = 384  $f_S$ , oversampling ratio =  $\times 128$ , 24-bit data, unless otherwise noted.

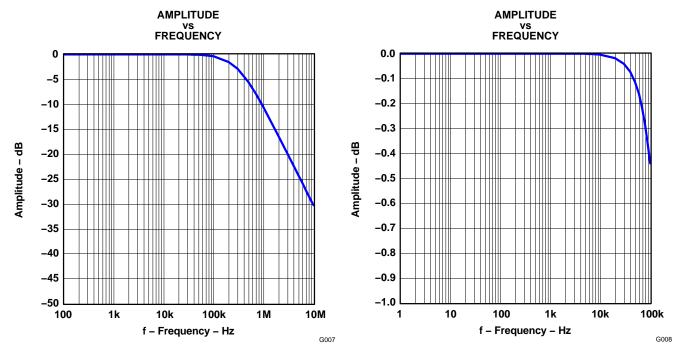

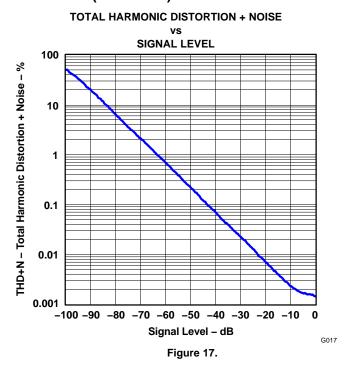

### **TYPICAL PERFORMANCE CURVES**

All specifications at  $T_A$  = 25°C,  $V_{CC}$  = 5 V,  $V_{DD}$  = 3.3 V, master mode,  $f_S$  = 44.1 kHz, system clock = 384  $f_S$ , oversampling ratio =  $\times 128$ , 24-bit data, unless otherwise noted.

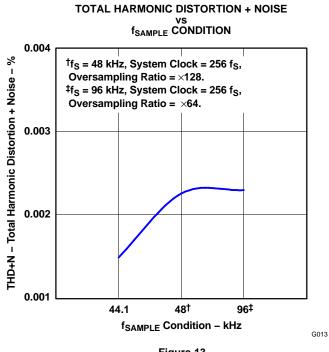

## **TYPICAL PERFORMANCE CURVES (continued)**

Figure 13.

Figure 14.

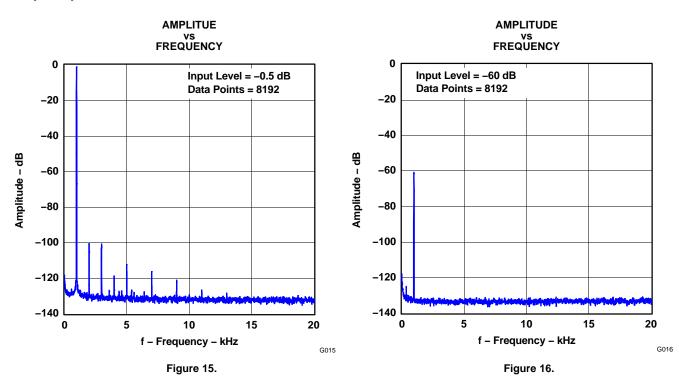

## **Output Spectrum**

All specifications at  $T_A$  = 25°C,  $V_{CC}$  = 5 V,  $V_{DD}$  = 3.3 V, master mode,  $f_S$  = 44.1 kHz, system clock = 384  $f_S$ , oversampling ratio =  $\times 128$ , 24-bit data, unless otherwise noted.

## **TYPICAL PERFORMANCE CURVES (continued)**

## **Supply Current**

All specifications at  $T_A$  = 25°C,  $V_{CC}$  = 5 V,  $V_{DD}$  = 3.3 V, master mode,  $f_S$  = 44.1 kHz, system clock = 384  $f_S$ , oversampling ratio =  $\times 128$ , 24-bit data, unless otherwise noted.

#### PRINCIPLES OF OPERATION

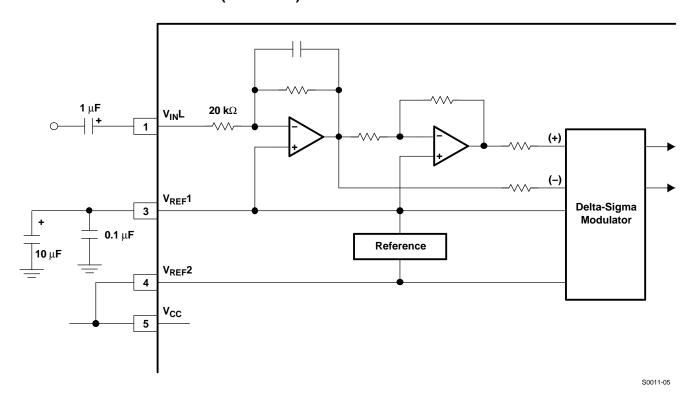

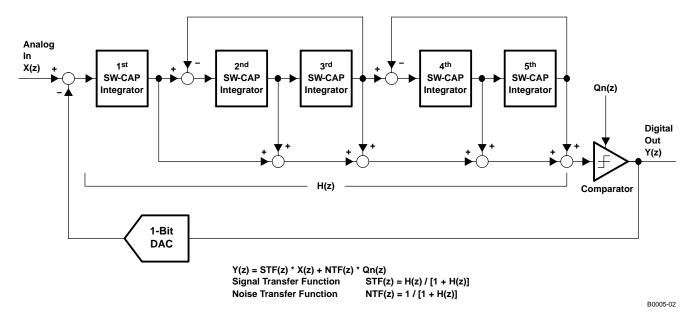

The PCM1802 consists of a reference circuit, two channels of single-ended-to-differential converter, a fifth-order delta-sigma modulator with full differential architecture, a decimation filter with high-pass filter, and a serial interface circuit. Figure 19 illustrates the total architecture of the PCM1802, Figure 20 illustrates the architecture of single-ended-to-differential converter and antialiasing filter, and Figure 21 is the block diagram of the fifth-order delta-sigma modulator and transfer function. An on-chip high-precision reference with one external capacitor provides all reference voltages that are needed in the PCM1802 and defines the full-scale voltage range for both channels. On-chip single-ended-to-differential signal converters save the design, space, and extra parts cost for external signal converters. Full-differential architecture provides a wide dynamic range and excellent power-supply rejection performance. The input signal is sampled at a ×64 or ×128 oversampling rate, thus eliminating an external sample-hold amplifier. A fifth-order delta-sigma noise shaper, which consists of five integrators using the switched capacitor technique and a comparator, shapes the quantization noise generated by the comparator and 1-bit DAC outside of the audio signal band. The high-order delta-sigma modulation randomizes the modulator outputs and reduces the idle tone level. The 64-f<sub>S</sub> or 128-f<sub>S</sub>, 1-bit stream from the delta-sigma modulator is converted to a 1-fs, 24-bit or 20-bit digital signal by removing high-frequency noise components with a decimation filter. The dc component of the signal is removed by the HPF, and the HPF output is converted to a time-multiplexed serial signal through the serial interface, which provides flexible serial formats.

Figure 19. Block Diagram

## **PRINCIPLES OF OPERATION (continued)**

Figure 20. Analog Front End (Left Channel)

Figure 21. Block Diagram of Fifth-Order Delta-Sigma Modulator

## PRINCIPLES OF OPERATION (continued)

#### System Clock

The PCM1802 supports 256  $f_S$ , 384  $f_S$ , 512  $f_S$ , and 768  $f_S$  as the system clock, where  $f_S$  is the audio sampling frequency. The system clock must be supplied on SCKI (pin 15).

The PCM1802 has a system clock detection circuit which automatically senses if the system clock is operating at 256  $f_S$ , 384  $f_S$ , 512  $f_S$ , or 768  $f_S$  in slave mode. In master mode, the system clock frequency must be selected by MODE0 (pin 19) and MODE1 (pin 20), and 768  $f_S$  is not available. For system clock inputs of 384  $f_S$ , 512  $f_S$ , and 768  $f_S$ , the system clock is divided to 256  $f_S$  automatically, and the 256  $f_S$  clock is used to operate the delta-sigma modulator and the digital filter.

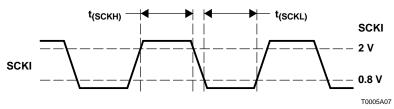

Table 1 shows the relationship of typical sampling frequencies and system clock frequencies, and Figure 22 shows system clock timing.

**SAMPLING RATE** SYSTEM CLOCK FREQUENCY (MHz) **FREQUENCY** 256 f<sub>S</sub> 384 f<sub>S</sub> 512 f<sub>S</sub> 768 f<sub>S</sub> (kHz) 32 8.192 12.288 16.384 24.576 44.1 11.2896 16.9344 22.5792 33.8688 48 12.288 18.432 24.576 36.864 64 16.384 24.576 32.768 49.152 88.2 22.5792 33.8688 45.1584 96 24.576 49.152 36.864

**Table 1. Sampling Frequency and System Clock Frequency**

|                     | PARAMETER                         |   |  |    |

|---------------------|-----------------------------------|---|--|----|

| t <sub>(SCKH)</sub> | System clock-pulse duration, high | 7 |  | ns |

| t <sub>(SCKL)</sub> | System clock-pulse duration, low  | 7 |  | ns |

Figure 22. System Clock Timing

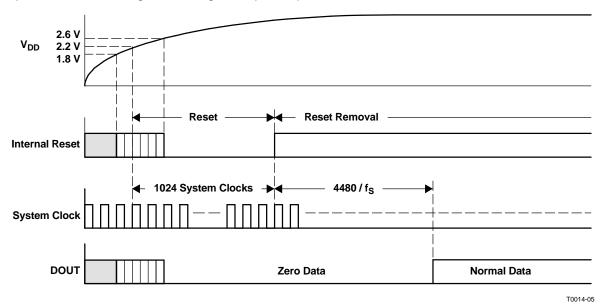

## **Power-On Reset Sequence**

The PCM1802 has an internal power-on reset circuit, and initialization (reset) is performed automatically when the power supply ( $V_{DD}$ ) exceeds 2.2 V (typical). While  $V_{DD}$  < 2.2 V (typical), and for 1024 system-clock counts after  $V_{DD}$  > 2.2 V (typical), the PCM1802 stays in the reset state and the digital output is forced to zero. The digital output is valid after the reset state is released and the time of 4480/f<sub>S</sub> has passed. Figure 23 illustrates the internal power-on reset timing and the digital output for power-on reset.

Figure 23. Internal Power-On Reset Timing

#### **Serial Audio Data Interface**

The PCM1802 interfaces with the audio system through BCK (pin 11), LRCK (pin 10), FSYNC (pin 9), and DOUT (pin 12).

#### **Interface Mode**

The PCM1802 supports master mode and slave mode as interface modes, and they are selected by MODE1 (pin 20) and MODE0 (pin 19) as shown in Table 2.

In master mode, the PCM1802 provides the timing for serial audio data communications between the PCM1802 and the digital audio processor or external circuit. In slave mode, the PCM1802 receives the timing for data transfer from an external controller.

**Table 2. Interface Mode**

| MODE1 | MODE0 | INTERFACE MODE                                                                                  |

|-------|-------|-------------------------------------------------------------------------------------------------|

| 0     | 0     | Slave mode (256 f <sub>S</sub> , 384 f <sub>S</sub> , 512 f <sub>S</sub> , 768 f <sub>S</sub> ) |

| 0     | 1     | Master mode (512 f <sub>S</sub> )                                                               |

| 1     | 0     | Master mode (384 f <sub>S</sub> )                                                               |

| 1     | 1     | Master mode (256 f <sub>S</sub> )                                                               |

#### Master mode

In master mode, BCK, LRCK, and FSYNC work as output pins, and these pins are controlled by timing which is generated in the clock circuit of the PCM1802. FSYNC is used to designate the valid data from the PCM1802. The rising edge of FSYNC indicates the starting point of the converted audio data and the falling edge of this signal indicates the ending point of the data. The frequency of this signal is fixed at  $2 \times LRCK$ . The duty cycle ratio depends on data bit length. The frequency of BCK is fixed at  $64 \times LRCK$ . The 768 f<sub>S</sub> system clock is not available in master mode.

#### Slave mode

In slave mode, BCK, LRCK, and FSYNC work as input pins. FSYNC is used to enable the BCK signal, and the PCM1802 can shift out the converted data while FSYNC is HIGH. The PCM1802 accepts either the 64 BCK/LRCK or the 48 BCK/LRCK format. The delay of FSYNC from the LRCK transition must be within 16 BCKs for the 64 BCK/LRCK format and within 12 BCKs for the 48 BCK/LRCK format.

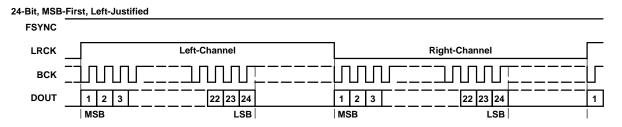

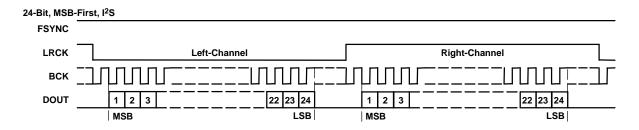

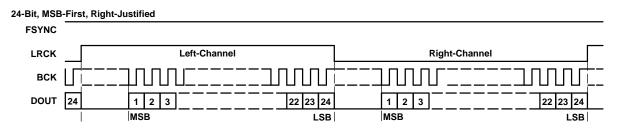

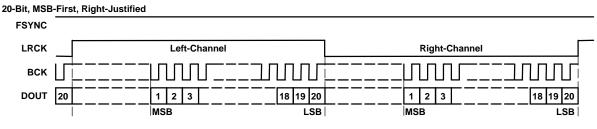

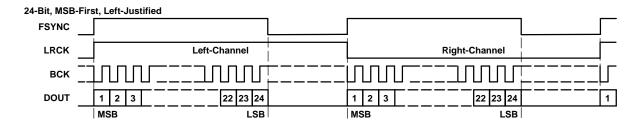

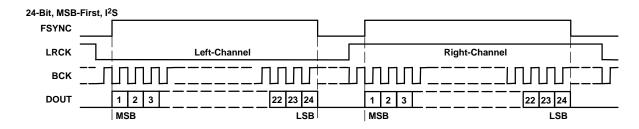

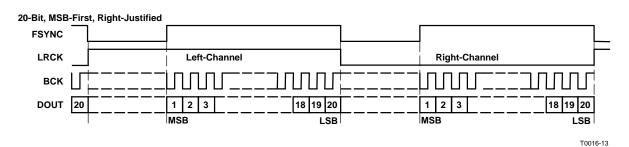

### **Data Format**

The PCM1802 supports four audio data formats in both master and slave modes, and they are selected by FMT1 (pin 18) and FMT0 (pin 17) as shown in Table 3. Figure 24 and Figure 26 illustrate the data formats in slave mode and master mode, respectively.

**Table 3. Data Format**

| FORMAT# | FMT1 | FMT0 | FORMAT                   |

|---------|------|------|--------------------------|

| 0       | 0    | 0    | Left-justified, 24-bit   |

| 1       | 0    | 1    | I <sup>2</sup> S, 24-bit |

| 2       | 1    | 0    | Right-justified, 24-bit  |

| 3       | 1    | 1    | Right-justified, 20-bit  |

## **Interface Timing**

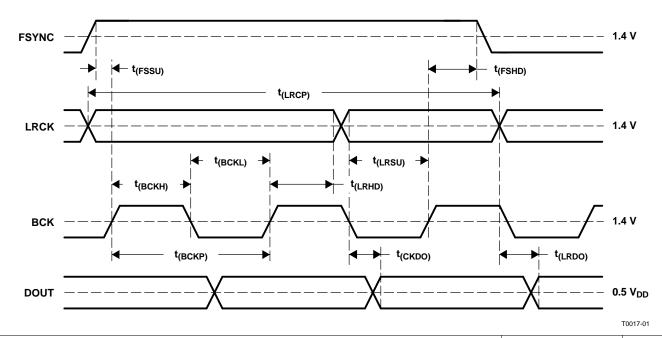

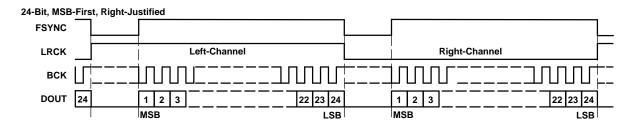

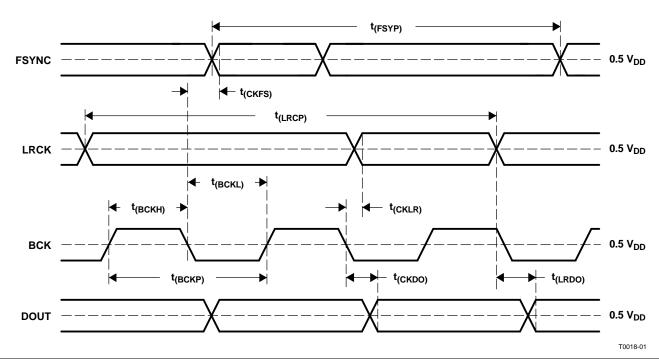

Figure 25 and Figure 27 illustrate the interface timing in slave mode and master mode, respectively.

## FORMAT 0: FMT[1:0] = 00

## FORMAT 1: FMT[1:0] = 01

## FORMAT 2: FMT[1:0] = 10

### FORMAT 3: FMT[1:0] = 11

T0016-12

Figure 24. Audio Data Format (Slave Mode: FSYNC, LRCK, and BCK Work as Inputs)

|                     | PARAMETER                                              |     |  |    | UNIT |

|---------------------|--------------------------------------------------------|-----|--|----|------|

| t <sub>(BCKP)</sub> | BCK period                                             | 150 |  |    | ns   |

| t <sub>(BCKH)</sub> | BCK pulse duration, high                               | 60  |  |    | ns   |

| t <sub>(BCKL)</sub> | BCK pulse duration, low                                | 60  |  |    | ns   |

| t <sub>(LRSU)</sub> | t <sub>(LRSU)</sub> LRCK setup time to BCK rising edge |     |  |    | ns   |

| t <sub>(LRHD)</sub> | LRCK hold time to BCK rising edge                      | 20  |  |    | ns   |

| t <sub>(LRCP)</sub> | LRCK period                                            | 10  |  |    | μs   |

| t <sub>(FSSU)</sub> | FSYNC setup time to BCK rising edge                    | 20  |  |    | ns   |

| t <sub>(FSHD)</sub> | FSYNC hold time to BCK rising edge                     | 20  |  |    | ns   |

| t <sub>(CKDO)</sub> | Delay time, BCK falling edge to DOUT valid             | -10 |  | 20 | ns   |

| t <sub>(LRDO)</sub> | Delay time, LRCK edge to DOUT valid                    | -10 |  | 20 | ns   |

| t <sub>r</sub>      | Rise time of all signals                               |     |  | 10 | ns   |

| t <sub>f</sub>      | Fall time of all signals                               |     |  | 10 | ns   |

NOTE: Timing measurement reference level is  $(V_{IH} + V_{IL})/2$ . Rise and fall times are measured from 10% to 90% of IN/OUT signal swing. Load capacitance of DOUT is 20 pF.

Figure 25. Audio Data Interface Timing (Slave Mode: FSYNC, LRCK, and BCK Work as Inputs)

## FORMAT 0: FMT[1:0] = 00

### FORMAT 1: FMT[1:0] = 01

## FORMAT 2: FMT[1:0] = 10

## FORMAT 3: FMT[1:0] = 11

Figure 26. Audio Data Format (Master Mode: FSYNC, LRCK, and BCK Work as Outputs)

|                     | PARAMETER                                   | MIN | TYP                    | MAX  | UNIT |

|---------------------|---------------------------------------------|-----|------------------------|------|------|

| t <sub>(BCKP)</sub> | BCK period                                  | 150 | 1/(64 f <sub>S</sub> ) | 1200 | ns   |

| t <sub>(BCKH)</sub> | BCK pulse duration, high                    | 75  |                        | 600  | ns   |

| t <sub>(BCKL)</sub> | BCK pulse duration, low                     | 75  |                        | 600  | ns   |

| t <sub>(CKLR)</sub> | Delay time, BCK falling edge to LRCK valid  | -10 |                        | 20   | ns   |

| t <sub>(LRCP)</sub> | LRCK period                                 | 10  | 1/f <sub>S</sub>       | 80   | μs   |

| t <sub>(CKFS)</sub> | Delay time, BCK falling edge to FSYNC valid | -10 |                        | 20   | ns   |

| t <sub>(FSYP)</sub> | FSYNC period                                | 5   | 1/(2 f <sub>S</sub> )  | 40   | μs   |

| t <sub>(CKDO)</sub> | Delay time, BCK falling edge to DOUT valid  | -10 |                        | 20   | ns   |

| t <sub>(LRDO)</sub> | Delay time, LRCK edge to DOUT valid         | -10 |                        | 20   | ns   |

| t <sub>r</sub>      | Rise time of all signals                    |     |                        | 10   | ns   |

| t <sub>f</sub>      | Fall time of all signals                    |     |                        | 10   | ns   |

NOTE: Timing measurement reference level is  $(V_{IH} + V_{IL}) / 2$ . Rise and fall times are measured from 10% to 90% of IN/OUT signal swing. Load capacitance of all signals is 20 pF.

Figure 27. Audio Data Interface Timing (Master Mode: FSYNC, LRCK, and BCK Work as Outputs)

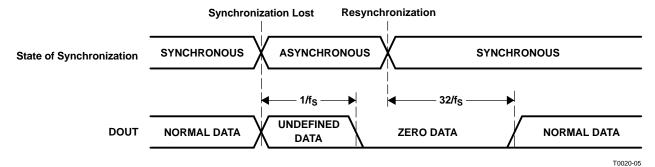

#### Synchronization With Digital Audio System

In slave mode, the PCM1802 operates under LRCK, synchronized with system clock SCKI. The PCM1802 does not need a specific phase relationship between LRCK and SCKI, but does require the synchronization of LRCK and SCKI.

If the relationship between LRCK and SCKI changes more than  $\pm 6$  BCKs for 64 BCK/frame ( $\pm 5$  BCKs for 48 BCK/frame) during one sample period due to LRCK or SCKI jitter, internal operation of the ADC halts within  $1/f_S$  and digital output is forced into BPZ code until resynchronization between LRCK and SCKI is completed.

In the case of changes less than ±5 BCKs for 64 BCK/frame (±4 BCKs for 48 BCK/frame), resynchronization does not occur.

Figure 28 illustrates the digital output response for loss of synchronization and resynchronization. During undefined data, some noise might be generated in the audio signal. Also, the transition of normal to undefined data and undefined or zero data to normal creates a data discontinuity in the digital output, which can generate some noise in the audio signal.

It is recommended to set PDWN low to get stable analog performance when the sampling rate, interface mode, data format, or oversampling control is changed.

Figure 28. ADC Digital Output for Loss of Synchronization and Resynchronization

## Power Down, HPF Bypass, Oversampling Control

PDWN (pin 7) controls the entire ADC operation. During power-down mode, both the supply current for the analog portion and the clock signal for the digital portion are shut down, and power dissipation is minimized. Also, DOUT (pin 12) is disabled and no system clock is accepted during power-down mode.

#### **Power-Down Control**

| PDWN | MODE                  |

|------|-----------------------|

| LOW  | Power-down mode       |

| HIGH | Normal operation mode |

The built-in function for dc component rejection can be bypassed using the BYPAS (pin 8) control. In bypass mode, the dc components of the analog input signal, internal dc offset, etc., are also converted and included in the digital output data.

### **HPF Bypass Control**

| BYPAS | HPF (HIGH-PASS FILTER) MODE           |

|-------|---------------------------------------|

| LOW   | Normal (no dc component on DOUT) mode |

| HIGH  | Bypass (dc component on DOUT) mode    |

OSR (pin 16) controls the oversampling ratio of the delta-sigma modulator, ×64 or ×128. The ×128 mode is available for f<sub>S</sub> < 50 kHz, and must be used carefully as performance is affected by the duty cycle of the 384 f<sub>S</sub> system clock.

## **Oversampling Control**

| OSR  | OVERSAMPLING RATIO             |

|------|--------------------------------|

| LOW  | ×64                            |

| HIGH | ×128 (f <sub>S</sub> < 50 kHz) |

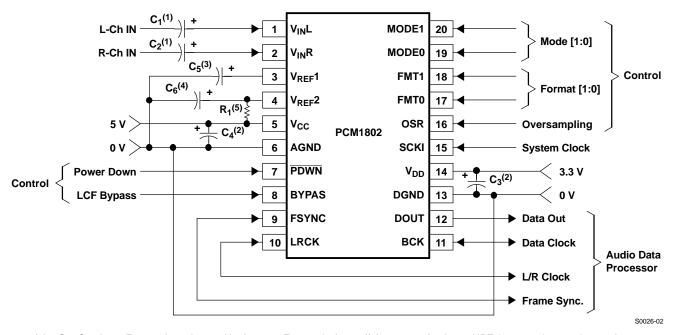

#### **APPLICATION INFORMATION**

## **Typical Circuit Connection Diagram**

Figure 29 illustrates a typical circuit connection diagram in which the cutoff frequency of the input HPF is about 8 Hz.

- (1)  $C_1$ ,  $C_2$ : A 1- $\mu$ F capacitor gives 8-Hz ( $\tau = 1 \mu$ F  $\times$  20 k $\Omega$ ) cutoff frequency for input HPF in normal operation and requires a power-on settling time with a 20-ms time constant during the power-on initialization period.

- (2) C<sub>3</sub>, C<sub>4</sub>: Bypass capacitors, 0.1-μF ceramic and 10-μF tantalum, depending on layout and power supply

- (3)  $C_5$ : 0.1- $\mu$ F ceramic and 10- $\mu$ F tantalum capacitors are recommended.

- (4) C<sub>6</sub>: 0.1-μF ceramic and 10-μF tantalum capacitors are recommended when using a noisy analog power supply. These capacitor are not required for a clean analog supply.

- (5) R<sub>1</sub>: A 1-kΩ resistor is recommended when using a noisy analog power supply. This resistor is shorted for a clean analog supply.

Figure 29. Typical Circuit Connection

## **APPLICATION INFORMATION (continued) Board Design and Layout Considerations**

### V<sub>CC</sub>, V<sub>DD</sub> Pins

The digital and analog power supply lines to the PCM1802 should be bypassed to the corresponding ground pins with 0.1- $\mu F$  ceramic and 10- $\mu F$  tantalum capacitors as close to the pins as possible to maximize the dynamic performance of the ADC.

## **AGND, DGND Pins**

To maximize the dynamic performance of the PCM1802, the analog and digital grounds are not connected internally. These grounds should have low impedance to avoid digital noise feeding back into the analog ground. They should be connected directly to each other under the parts to reduce the potential noise problem.

## **VIN Pins**

A 1- $\mu$ F capacitor is recommended as an ac-coupling capacitor, which gives an 8-Hz cutoff frequency. If a higher full-scale input voltage is required, it can be accommodated by adding only one series resistor to each  $V_{IN}$  pin.

## V<sub>REF</sub>1 Pin

A ceramic capacitor of 0.1  $\mu$ F and an electrolytic capacitor of 10  $\mu$ F are recommended between V<sub>REF</sub>1 and AGND to ensure low source impedance for the ADC references. These capacitors should be located as close as possible to the V<sub>REF</sub>1 pin to reduce dynamic errors on the ADC references.

#### V<sub>RFF</sub>2 Pin

The differential voltage between  $V_{REF}2$  and AGND sets the analog input full-scale range. A ceramic capacitor of 0.1  $\mu$ F and an electrolytic capacitor of 10  $\mu$ F are recommended between  $V_{REF}2$  and AGND with the insertion of a 1-k $\Omega$  resistor between  $V_{CC}$  and  $V_{REF}2$  when using a noisy analog power supply. These capacitors and resistor are not required for a clean analog supply. These capacitors should be located as close as possible to the  $V_{REF}2$  pin to reduce dynamic errors on the ADC references. Full-scale input level is affected by this 1-k $\Omega$  resistor, decreasing by 3%.

#### **DOUT Pin**

The DOUT pin has enough load drive capability, but locating a buffer near the PCM1802 and minimizing load capacitance is recommended if the DOUT line is long, in order to minimize the digital-analog crosstalk and maximize the dynamic performance of the ADC.

#### **System Clock**

The quality of the system clock can influence dynamic performance, as the PCM1802 operates based on the system clock. In slave mode, it may be necessary to consider the system-clock duty cycle, jitter, and the time difference between the system clock transition and the BCK or LRCK transition.

.com 14-Oct-2008

#### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan <sup>(2)</sup>    | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|----------------------------|------------------|------------------------------|

| PCM1802DB        | ACTIVE                | SSOP            | DB                 | 20   | 65             | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-1-260C-UNLIM           |

| PCM1802DBG4      | ACTIVE                | SSOP            | DB                 | 20   | 65             | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM           |

| PCM1802DBR       | ACTIVE                | SSOP            | DB                 | 20   | 2000           | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM           |

| PCM1802DBRG4     | ACTIVE                | SSOP            | DB                 | 20   | 2000           | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM           |

| PCM1802S1DB      | OBSOLETE              | SSOP            | DB                 | 20   |                | TBD                        | Call TI          | Call TI                      |

| PCM1802S1DBG4    | OBSOLETE              | SSOP            | DB                 | 20   |                | TBD                        | Call TI          | Call TI                      |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

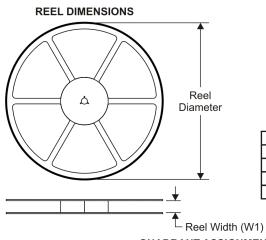

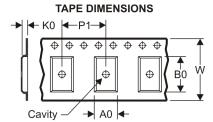

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

|    | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

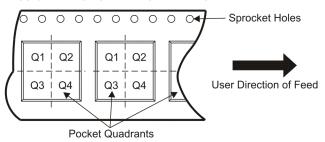

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

### \*All dimensions are nominal

| Device     |      | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------|------|--------------------|----|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

| PCM1802DBR | SSOP | DB                 | 20 | 2000 | 330.0                    | 17.4                     | 8.5     | 7.6     | 2.4     | 12.0       | 16.0      | Q1               |

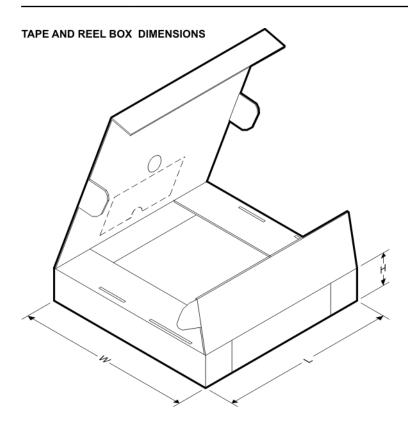

#### \*All dimensions are nominal

| Ī | Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---|------------|--------------|-----------------|------|------|-------------|------------|-------------|

|   | PCM1802DBR | SSOP         | DB              | 20   | 2000 | 336.6       | 336.6      | 28.6        |

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

#### **Products Amplifiers** amplifier.ti.com Data Converters dataconverter.ti.com DSP dsp.ti.com Clocks and Timers www.ti.com/clocks Interface interface.ti.com Logic logic.ti.com Power Mgmt power.ti.com Microcontrollers microcontroller.ti.com www.ti-rfid.com RF/IF and ZigBee® Solutions www.ti.com/lprf

| Applications       |                           |

|--------------------|---------------------------|

| Audio              | www.ti.com/audio          |

| Automotive         | www.ti.com/automotive     |

| Broadband          | www.ti.com/broadband      |

| Digital Control    | www.ti.com/digitalcontrol |

| Medical            | www.ti.com/medical        |

| Military           | www.ti.com/military       |

| Optical Networking | www.ti.com/opticalnetwork |

| Security           | www.ti.com/security       |

| Telephony          | www.ti.com/telephony      |

| Video & Imaging    | www.ti.com/video          |

| Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2008, Texas Instruments Incorporated